|

| | R600TTIImpl (const AMDGPUTargetMachine *TM, const Function &F) |

| |

| const R600Subtarget * | getST () const |

| |

| const AMDGPUTargetLowering * | getTLI () const |

| |

| void | getUnrollingPreferences (Loop *L, ScalarEvolution &SE, TTI::UnrollingPreferences &UP) |

| |

| unsigned | getHardwareNumberOfRegisters (bool Vec) const |

| |

| unsigned | getNumberOfRegisters (bool Vec) const |

| |

| unsigned | getRegisterBitWidth (bool Vector) const |

| |

| unsigned | getMinVectorRegisterBitWidth () const |

| |

| unsigned | getLoadStoreVecRegBitWidth (unsigned AddrSpace) const |

| |

| bool | isLegalToVectorizeMemChain (unsigned ChainSizeInBytes, unsigned Alignment, unsigned AddrSpace) const |

| |

| bool | isLegalToVectorizeLoadChain (unsigned ChainSizeInBytes, unsigned Alignment, unsigned AddrSpace) const |

| |

| bool | isLegalToVectorizeStoreChain (unsigned ChainSizeInBytes, unsigned Alignment, unsigned AddrSpace) const |

| |

| unsigned | getMaxInterleaveFactor (unsigned VF) |

| |

| unsigned | getCFInstrCost (unsigned Opcode) |

| |

| int | getVectorInstrCost (unsigned Opcode, Type *ValTy, unsigned Index) |

| |

| bool | allowsMisalignedMemoryAccesses (LLVMContext &Context, unsigned BitWidth, unsigned AddressSpace, unsigned Alignment, bool *Fast) const |

| |

| bool | hasBranchDivergence () |

| |

| bool | isSourceOfDivergence (const Value *V) |

| |

| bool | isAlwaysUniform (const Value *V) |

| |

| unsigned | getFlatAddressSpace () |

| |

| bool | isLegalAddImmediate (int64_t imm) |

| |

| bool | isLegalICmpImmediate (int64_t imm) |

| |

| bool | isLegalAddressingMode (Type *Ty, GlobalValue *BaseGV, int64_t BaseOffset, bool HasBaseReg, int64_t Scale, unsigned AddrSpace, Instruction *I=nullptr) |

| |

| bool | isIndexedLoadLegal (TTI::MemIndexedMode M, Type *Ty, const DataLayout &DL) const |

| |

| bool | isIndexedStoreLegal (TTI::MemIndexedMode M, Type *Ty, const DataLayout &DL) const |

| |

| bool | isLSRCostLess (TTI::LSRCost C1, TTI::LSRCost C2) |

| |

| int | getScalingFactorCost (Type *Ty, GlobalValue *BaseGV, int64_t BaseOffset, bool HasBaseReg, int64_t Scale, unsigned AddrSpace) |

| |

| bool | isTruncateFree (Type *Ty1, Type *Ty2) |

| |

| bool | isProfitableToHoist (Instruction *I) |

| |

| bool | useAA () const |

| |

| bool | isTypeLegal (Type *Ty) |

| |

| int | getGEPCost (Type *PointeeType, const Value *Ptr, ArrayRef< const Value * > Operands) |

| |

| int | getExtCost (const Instruction *I, const Value *Src) |

| |

| unsigned | getIntrinsicCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< const Value * > Arguments) |

| |

| unsigned | getIntrinsicCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< Type * > ParamTys) |

| |

| unsigned | getEstimatedNumberOfCaseClusters (const SwitchInst &SI, unsigned &JumpTableSize) |

| |

| unsigned | getJumpBufAlignment () |

| |

| unsigned | getJumpBufSize () |

| |

| bool | shouldBuildLookupTables () |

| |

| bool | haveFastSqrt (Type *Ty) |

| |

| bool | isFCmpOrdCheaperThanFCmpZero (Type *Ty) |

| |

| unsigned | getFPOpCost (Type *Ty) |

| |

| unsigned | getOperationCost (unsigned Opcode, Type *Ty, Type *OpTy) |

| |

| unsigned | getInliningThresholdMultiplier () |

| |

| void | getUnrollingPreferences (Loop *L, ScalarEvolution &SE, TTI::UnrollingPreferences &UP) |

| |

| int | getInstructionLatency (const Instruction *I) |

| |

| unsigned | getNumberOfRegisters (bool Vector) |

| |

| unsigned | getRegisterBitWidth (bool Vector) const |

| |

| unsigned | getScalarizationOverhead (Type *Ty, bool Insert, bool Extract) |

| | Estimate the overhead of scalarizing an instruction. More...

|

| |

| unsigned | getScalarizationOverhead (Type *VecTy, ArrayRef< const Value * > Args) |

| |

| unsigned | getOperandsScalarizationOverhead (ArrayRef< const Value * > Args, unsigned VF) |

| | Estimate the overhead of scalarizing an instructions unique non-constant operands. More...

|

| |

| unsigned | getMaxInterleaveFactor (unsigned VF) |

| |

| unsigned | getArithmeticInstrCost (unsigned Opcode, Type *Ty, TTI::OperandValueKind Opd1Info=TTI::OK_AnyValue, TTI::OperandValueKind Opd2Info=TTI::OK_AnyValue, TTI::OperandValueProperties Opd1PropInfo=TTI::OP_None, TTI::OperandValueProperties Opd2PropInfo=TTI::OP_None, ArrayRef< const Value * > Args=ArrayRef< const Value * >()) |

| |

| unsigned | getShuffleCost (TTI::ShuffleKind Kind, Type *Tp, int Index, Type *SubTp) |

| |

| unsigned | getCastInstrCost (unsigned Opcode, Type *Dst, Type *Src, const Instruction *I=nullptr) |

| |

| unsigned | getExtractWithExtendCost (unsigned Opcode, Type *Dst, VectorType *VecTy, unsigned Index) |

| |

| unsigned | getCFInstrCost (unsigned Opcode) |

| |

| unsigned | getCmpSelInstrCost (unsigned Opcode, Type *ValTy, Type *CondTy, const Instruction *I) |

| |

| unsigned | getVectorInstrCost (unsigned Opcode, Type *Val, unsigned Index) |

| |

| unsigned | getMemoryOpCost (unsigned Opcode, Type *Src, unsigned Alignment, unsigned AddressSpace, const Instruction *I=nullptr) |

| |

| unsigned | getInterleavedMemoryOpCost (unsigned Opcode, Type *VecTy, unsigned Factor, ArrayRef< unsigned > Indices, unsigned Alignment, unsigned AddressSpace, bool UseMaskForCond=false, bool UseMaskForGaps=false) |

| |

| unsigned | getIntrinsicInstrCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< Value * > Args, FastMathFlags FMF, unsigned VF=1) |

| | Get intrinsic cost based on arguments. More...

|

| |

| unsigned | getIntrinsicInstrCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< Type * > Tys, FastMathFlags FMF, unsigned ScalarizationCostPassed=std::numeric_limits< unsigned >::max()) |

| | Get intrinsic cost based on argument types. More...

|

| |

| unsigned | getCallInstrCost (Function *F, Type *RetTy, ArrayRef< Type * > Tys) |

| | Compute a cost of the given call instruction. More...

|

| |

| unsigned | getNumberOfParts (Type *Tp) |

| |

| unsigned | getAddressComputationCost (Type *Ty, ScalarEvolution *, const SCEV *) |

| |

| unsigned | getArithmeticReductionCost (unsigned Opcode, Type *Ty, bool IsPairwise) |

| | Try to calculate arithmetic and shuffle op costs for reduction operations. More...

|

| |

| unsigned | getMinMaxReductionCost (Type *Ty, Type *CondTy, bool IsPairwise, bool) |

| | Try to calculate op costs for min/max reduction operations. More...

|

| |

| unsigned | getVectorSplitCost () |

| |

| unsigned | getCallCost (const Function *F, int NumArgs) |

| |

| unsigned | getCallCost (const Function *F, ArrayRef< const Value * > Arguments) |

| |

| int | getGEPCost (Type *PointeeType, const Value *Ptr, ArrayRef< const Value * > Operands) |

| |

| unsigned | getIntrinsicCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< const Value * > Arguments) |

| |

| unsigned | getUserCost (const User *U, ArrayRef< const Value * > Operands) |

| |

| int | getInstructionLatency (const Instruction *I) |

| |

| | TargetTransformInfoImplBase (const TargetTransformInfoImplBase &Arg) |

| |

| | TargetTransformInfoImplBase (TargetTransformInfoImplBase &&Arg) |

| |

| const DataLayout & | getDataLayout () const |

| |

| unsigned | getOperationCost (unsigned Opcode, Type *Ty, Type *OpTy) |

| |

| int | getGEPCost (Type *PointeeType, const Value *Ptr, ArrayRef< const Value *> Operands) |

| |

| unsigned | getEstimatedNumberOfCaseClusters (const SwitchInst &SI, unsigned &JTSize) |

| |

| int | getExtCost (const Instruction *I, const Value *Src) |

| |

| unsigned | getCallCost (FunctionType *FTy, int NumArgs) |

| |

| unsigned | getInliningThresholdMultiplier () |

| |

| unsigned | getIntrinsicCost (Intrinsic::ID IID, Type *RetTy, ArrayRef< Type *> ParamTys) |

| |

| bool | hasBranchDivergence () |

| |

| bool | isSourceOfDivergence (const Value *V) |

| |

| bool | isAlwaysUniform (const Value *V) |

| |

| unsigned | getFlatAddressSpace () |

| |

| bool | isLoweredToCall (const Function *F) |

| |

| void | getUnrollingPreferences (Loop *, ScalarEvolution &, TTI::UnrollingPreferences &) |

| |

| bool | isLegalAddImmediate (int64_t Imm) |

| |

| bool | isLegalICmpImmediate (int64_t Imm) |

| |

| bool | isLegalAddressingMode (Type *Ty, GlobalValue *BaseGV, int64_t BaseOffset, bool HasBaseReg, int64_t Scale, unsigned AddrSpace, Instruction *I=nullptr) |

| |

| bool | isLSRCostLess (TTI::LSRCost &C1, TTI::LSRCost &C2) |

| |

| bool | canMacroFuseCmp () |

| |

| bool | shouldFavorPostInc () const |

| |

| bool | isLegalMaskedStore (Type *DataType) |

| |

| bool | isLegalMaskedLoad (Type *DataType) |

| |

| bool | isLegalMaskedScatter (Type *DataType) |

| |

| bool | isLegalMaskedGather (Type *DataType) |

| |

| bool | hasDivRemOp (Type *DataType, bool IsSigned) |

| |

| bool | hasVolatileVariant (Instruction *I, unsigned AddrSpace) |

| |

| bool | prefersVectorizedAddressing () |

| |

| int | getScalingFactorCost (Type *Ty, GlobalValue *BaseGV, int64_t BaseOffset, bool HasBaseReg, int64_t Scale, unsigned AddrSpace) |

| |

| bool | LSRWithInstrQueries () |

| |

| bool | isTruncateFree (Type *Ty1, Type *Ty2) |

| |

| bool | isProfitableToHoist (Instruction *I) |

| |

| bool | useAA () |

| |

| bool | isTypeLegal (Type *Ty) |

| |

| unsigned | getJumpBufAlignment () |

| |

| unsigned | getJumpBufSize () |

| |

| bool | shouldBuildLookupTables () |

| |

| bool | shouldBuildLookupTablesForConstant (Constant *C) |

| |

| bool | useColdCCForColdCall (Function &F) |

| |

| unsigned | getScalarizationOverhead (Type *Ty, bool Insert, bool Extract) |

| |

| unsigned | getOperandsScalarizationOverhead (ArrayRef< const Value *> Args, unsigned VF) |

| |

| bool | supportsEfficientVectorElementLoadStore () |

| |

| bool | enableAggressiveInterleaving (bool LoopHasReductions) |

| |

| const TTI::MemCmpExpansionOptions * | enableMemCmpExpansion (bool IsZeroCmp) const |

| |

| bool | enableInterleavedAccessVectorization () |

| |

| bool | enableMaskedInterleavedAccessVectorization () |

| |

| bool | isFPVectorizationPotentiallyUnsafe () |

| |

| bool | allowsMisalignedMemoryAccesses (LLVMContext &Context, unsigned BitWidth, unsigned AddressSpace, unsigned Alignment, bool *Fast) |

| |

| TTI::PopcntSupportKind | getPopcntSupport (unsigned IntTyWidthInBit) |

| |

| bool | haveFastSqrt (Type *Ty) |

| |

| bool | isFCmpOrdCheaperThanFCmpZero (Type *Ty) |

| |

| unsigned | getFPOpCost (Type *Ty) |

| |

| int | getIntImmCodeSizeCost (unsigned Opcode, unsigned Idx, const APInt &Imm, Type *Ty) |

| |

| unsigned | getIntImmCost (const APInt &Imm, Type *Ty) |

| |

| unsigned | getIntImmCost (unsigned Opcode, unsigned Idx, const APInt &Imm, Type *Ty) |

| |

| unsigned | getIntImmCost (Intrinsic::ID IID, unsigned Idx, const APInt &Imm, Type *Ty) |

| |

| unsigned | getNumberOfRegisters (bool Vector) |

| |

| unsigned | getRegisterBitWidth (bool Vector) const |

| |

| unsigned | getMinVectorRegisterBitWidth () |

| |

| bool | shouldMaximizeVectorBandwidth (bool OptSize) const |

| |

| unsigned | getMinimumVF (unsigned ElemWidth) const |

| |

| bool | shouldConsiderAddressTypePromotion (const Instruction &I, bool &AllowPromotionWithoutCommonHeader) |

| |

| unsigned | getCacheLineSize () |

| |

| llvm::Optional< unsigned > | getCacheSize (TargetTransformInfo::CacheLevel Level) |

| |

| llvm::Optional< unsigned > | getCacheAssociativity (TargetTransformInfo::CacheLevel Level) |

| |

| unsigned | getPrefetchDistance () |

| |

| unsigned | getMinPrefetchStride () |

| |

| unsigned | getMaxPrefetchIterationsAhead () |

| |

| unsigned | getMaxInterleaveFactor (unsigned VF) |

| |

| unsigned | getArithmeticInstrCost (unsigned Opcode, Type *Ty, TTI::OperandValueKind Opd1Info, TTI::OperandValueKind Opd2Info, TTI::OperandValueProperties Opd1PropInfo, TTI::OperandValueProperties Opd2PropInfo, ArrayRef< const Value *> Args) |

| |

| unsigned | getShuffleCost (TTI::ShuffleKind Kind, Type *Ty, int Index, Type *SubTp) |

| |

| unsigned | getCastInstrCost (unsigned Opcode, Type *Dst, Type *Src, const Instruction *I) |

| |

| unsigned | getExtractWithExtendCost (unsigned Opcode, Type *Dst, VectorType *VecTy, unsigned Index) |

| |

| unsigned | getCFInstrCost (unsigned Opcode) |

| |

| unsigned | getCmpSelInstrCost (unsigned Opcode, Type *ValTy, Type *CondTy, const Instruction *I) |

| |

| unsigned | getVectorInstrCost (unsigned Opcode, Type *Val, unsigned Index) |

| |

| unsigned | getMemoryOpCost (unsigned Opcode, Type *Src, unsigned Alignment, unsigned AddressSpace, const Instruction *I) |

| |

| unsigned | getMaskedMemoryOpCost (unsigned Opcode, Type *Src, unsigned Alignment, unsigned AddressSpace) |

| |

| unsigned | getGatherScatterOpCost (unsigned Opcode, Type *DataTy, Value *Ptr, bool VariableMask, unsigned Alignment) |

| |

| unsigned | getInterleavedMemoryOpCost (unsigned Opcode, Type *VecTy, unsigned Factor, ArrayRef< unsigned > Indices, unsigned Alignment, unsigned AddressSpace, bool UseMaskForCond=false, bool UseMaskForGaps=false) |

| |

| unsigned | getIntrinsicInstrCost (Intrinsic::ID ID, Type *RetTy, ArrayRef< Type *> Tys, FastMathFlags FMF, unsigned ScalarizationCostPassed) |

| |

| unsigned | getIntrinsicInstrCost (Intrinsic::ID ID, Type *RetTy, ArrayRef< Value *> Args, FastMathFlags FMF, unsigned VF) |

| |

| unsigned | getCallInstrCost (Function *F, Type *RetTy, ArrayRef< Type *> Tys) |

| |

| unsigned | getNumberOfParts (Type *Tp) |

| |

| unsigned | getAddressComputationCost (Type *Tp, ScalarEvolution *, const SCEV *) |

| |

| unsigned | getArithmeticReductionCost (unsigned, Type *, bool) |

| |

| unsigned | getMinMaxReductionCost (Type *, Type *, bool, bool) |

| |

| unsigned | getCostOfKeepingLiveOverCall (ArrayRef< Type *> Tys) |

| |

| bool | getTgtMemIntrinsic (IntrinsicInst *Inst, MemIntrinsicInfo &Info) |

| |

| unsigned | getAtomicMemIntrinsicMaxElementSize () const |

| |

| Value * | getOrCreateResultFromMemIntrinsic (IntrinsicInst *Inst, Type *ExpectedType) |

| |

| Type * | getMemcpyLoopLoweringType (LLVMContext &Context, Value *Length, unsigned SrcAlign, unsigned DestAlign) const |

| |

| void | getMemcpyLoopResidualLoweringType (SmallVectorImpl< Type *> &OpsOut, LLVMContext &Context, unsigned RemainingBytes, unsigned SrcAlign, unsigned DestAlign) const |

| |

| bool | areInlineCompatible (const Function *Caller, const Function *Callee) const |

| |

| bool | areFunctionArgsABICompatible (const Function *Caller, const Function *Callee, SmallPtrSetImpl< Argument *> &Args) const |

| |

| bool | isIndexedLoadLegal (TTI::MemIndexedMode Mode, Type *Ty, const DataLayout &DL) const |

| |

| bool | isIndexedStoreLegal (TTI::MemIndexedMode Mode, Type *Ty, const DataLayout &DL) const |

| |

| unsigned | getLoadStoreVecRegBitWidth (unsigned AddrSpace) const |

| |

| bool | isLegalToVectorizeLoad (LoadInst *LI) const |

| |

| bool | isLegalToVectorizeStore (StoreInst *SI) const |

| |

| bool | isLegalToVectorizeLoadChain (unsigned ChainSizeInBytes, unsigned Alignment, unsigned AddrSpace) const |

| |

| bool | isLegalToVectorizeStoreChain (unsigned ChainSizeInBytes, unsigned Alignment, unsigned AddrSpace) const |

| |

| unsigned | getLoadVectorFactor (unsigned VF, unsigned LoadSize, unsigned ChainSizeInBytes, VectorType *VecTy) const |

| |

| unsigned | getStoreVectorFactor (unsigned VF, unsigned StoreSize, unsigned ChainSizeInBytes, VectorType *VecTy) const |

| |

| bool | useReductionIntrinsic (unsigned Opcode, Type *Ty, TTI::ReductionFlags Flags) const |

| |

| bool | shouldExpandReduction (const IntrinsicInst *II) const |

| |

Protected Types inherited from llvm::TargetTransformInfoImplBase

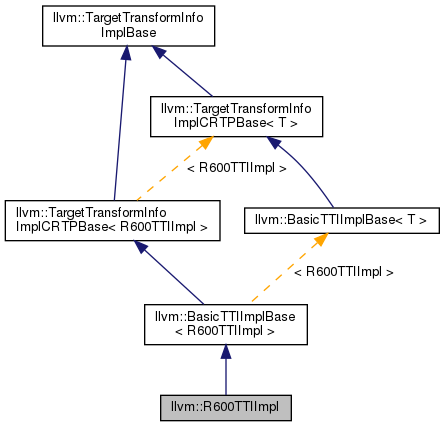

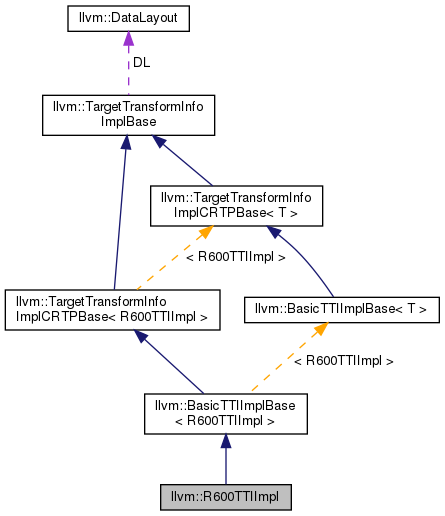

Protected Types inherited from llvm::TargetTransformInfoImplBase Protected Member Functions inherited from llvm::BasicTTIImplBase< R600TTIImpl >

Protected Member Functions inherited from llvm::BasicTTIImplBase< R600TTIImpl > Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< R600TTIImpl >

Protected Member Functions inherited from llvm::TargetTransformInfoImplCRTPBase< R600TTIImpl > Protected Member Functions inherited from llvm::TargetTransformInfoImplBase

Protected Member Functions inherited from llvm::TargetTransformInfoImplBase Protected Attributes inherited from llvm::TargetTransformInfoImplBase

Protected Attributes inherited from llvm::TargetTransformInfoImplBase 1.8.13

1.8.13