#include "HexagonTargetMachine.h"#include "Hexagon.h"#include "HexagonISelLowering.h"#include "HexagonMachineScheduler.h"#include "HexagonTargetObjectFile.h"#include "HexagonTargetTransformInfo.h"#include "llvm/CodeGen/Passes.h"#include "llvm/CodeGen/TargetPassConfig.h"#include "llvm/IR/LegacyPassManager.h"#include "llvm/IR/Module.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/TargetRegistry.h"#include "llvm/Transforms/IPO/PassManagerBuilder.h"#include "llvm/Transforms/Scalar.h"

Go to the source code of this file.

Namespaces | |

| llvm | |

| This class represents lattice values for constants. | |

Variables | |

| static cl::opt< bool > | EnableCExtOpt ("hexagon-cext", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Enable Hexagon constant-extender optimization")) |

| static cl::opt< bool > | EnableRDFOpt ("rdf-opt", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Enable RDF-based optimizations")) |

| static cl::opt< bool > | DisableHardwareLoops ("disable-hexagon-hwloops", cl::Hidden, cl::desc("Disable Hardware Loops for Hexagon target")) |

| static cl::opt< bool > | DisableAModeOpt ("disable-hexagon-amodeopt", cl::Hidden, cl::ZeroOrMore, cl::init(false), cl::desc("Disable Hexagon Addressing Mode Optimization")) |

| static cl::opt< bool > | DisableHexagonCFGOpt ("disable-hexagon-cfgopt", cl::Hidden, cl::ZeroOrMore, cl::init(false), cl::desc("Disable Hexagon CFG Optimization")) |

| static cl::opt< bool > | DisableHCP ("disable-hcp", cl::init(false), cl::Hidden, cl::ZeroOrMore, cl::desc("Disable Hexagon constant propagation")) |

| static cl::opt< bool > | DisableStoreWidening ("disable-store-widen", cl::Hidden, cl::init(false), cl::desc("Disable store widening")) |

| static cl::opt< bool > | EnableExpandCondsets ("hexagon-expand-condsets", cl::init(true), cl::Hidden, cl::ZeroOrMore, cl::desc("Early expansion of MUX")) |

| static cl::opt< bool > | EnableEarlyIf ("hexagon-eif", cl::init(true), cl::Hidden, cl::ZeroOrMore, cl::desc("Enable early if-conversion")) |

| static cl::opt< bool > | EnableGenInsert ("hexagon-insert", cl::init(true), cl::Hidden, cl::desc("Generate \nsert\instructions")) |

| static cl::opt< bool > | EnableCommGEP ("hexagon-commgep", cl::init(true), cl::Hidden, cl::ZeroOrMore, cl::desc("Enable commoning of GEP instructions")) |

| static cl::opt< bool > | EnableGenExtract ("hexagon-extract", cl::init(true), cl::Hidden, cl::desc("Generate \xtract\instructions")) |

| static cl::opt< bool > | EnableGenMux ("hexagon-mux", cl::init(true), cl::Hidden, cl::desc("Enable converting conditional transfers into MUX instructions")) |

| static cl::opt< bool > | EnableGenPred ("hexagon-gen-pred", cl::init(true), cl::Hidden, cl::desc("Enable conversion of arithmetic operations to " "predicate instructions")) |

| static cl::opt< bool > | EnableLoopPrefetch ("hexagon-loop-prefetch", cl::init(false), cl::Hidden, cl::ZeroOrMore, cl::desc("Enable loop data prefetch on Hexagon")) |

| static cl::opt< bool > | DisableHSDR ("disable-hsdr", cl::init(false), cl::Hidden, cl::desc("Disable splitting double registers")) |

| static cl::opt< bool > | EnableBitSimplify ("hexagon-bit", cl::init(true), cl::Hidden, cl::desc("Bit simplification")) |

| static cl::opt< bool > | EnableLoopResched ("hexagon-loop-resched", cl::init(true), cl::Hidden, cl::desc("Loop rescheduling")) |

| static cl::opt< bool > | HexagonNoOpt ("hexagon-noopt", cl::init(false), cl::Hidden, cl::desc("Disable backend optimizations")) |

| static cl::opt< bool > | EnableVectorPrint ("enable-hexagon-vector-print", cl::Hidden, cl::ZeroOrMore, cl::init(false), cl::desc("Enable Hexagon Vector print instr pass")) |

| static cl::opt< bool > | EnableVExtractOpt ("hexagon-opt-vextract", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Enable vextract optimization")) |

| static cl::opt< bool > | EnableInitialCFGCleanup ("hexagon-initial-cfg-cleanup", cl::Hidden, cl::ZeroOrMore, cl::init(true), cl::desc("Simplify the CFG after atomic expansion pass")) |

| int | HexagonTargetMachineModule = 0 |

| HexagonTargetMachineModule - Note that this is used on hosts that cannot link in a library unless there are references into the library. More... | |

| static MachineSchedRegistry | SchedCustomRegistry ("hexagon", "Run Hexagon's custom scheduler", createVLIWMachineSched) |

Function Documentation

◆ createVLIWMachineSched()

|

static |

Definition at line 112 of file HexagonTargetMachine.cpp.

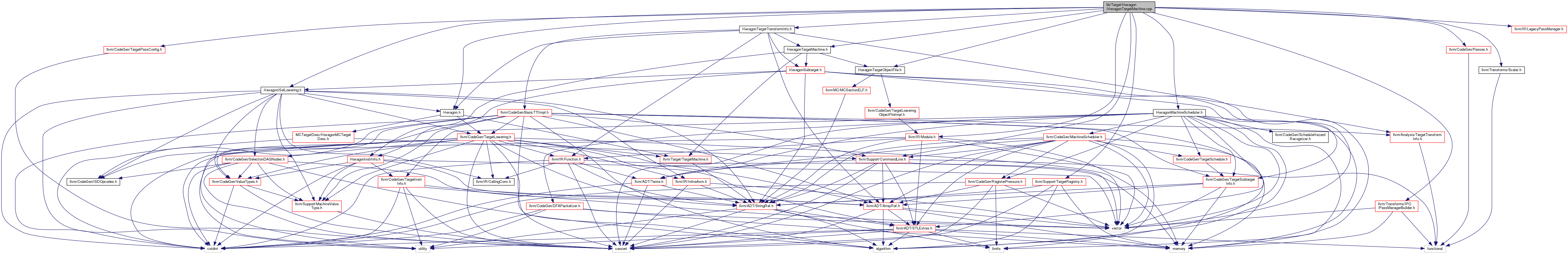

References llvm::ScheduleDAGMI::addMutation(), llvm::createCopyConstrainDAGMutation(), llvm::createHexagonBitSimplify(), llvm::createHexagonBranchRelaxation(), llvm::createHexagonCallFrameInformation(), llvm::createHexagonCFGOptimizer(), llvm::createHexagonCommonGEP(), llvm::createHexagonConstExtenders(), llvm::createHexagonConstPropagationPass(), llvm::createHexagonCopyToCombine(), llvm::createHexagonEarlyIfConversion(), llvm::createHexagonFixupHwLoops(), llvm::createHexagonGenExtract(), llvm::createHexagonGenInsert(), llvm::createHexagonGenMux(), llvm::createHexagonGenPredicate(), llvm::createHexagonHardwareLoops(), llvm::createHexagonISelDag(), llvm::createHexagonLoopIdiomPass(), llvm::createHexagonLoopRescheduling(), llvm::createHexagonNewValueJump(), llvm::createHexagonOptAddrMode(), llvm::createHexagonOptimizeSZextends(), llvm::createHexagonPacketizer(), llvm::createHexagonPeephole(), llvm::createHexagonRDFOpt(), llvm::createHexagonSplitConst32AndConst64(), llvm::createHexagonSplitDoubleRegs(), llvm::createHexagonStoreWidening(), llvm::createHexagonVectorLoopCarriedReusePass(), llvm::createHexagonVectorPrint(), llvm::createHexagonVExtract(), llvm::HexagonExpandCondsetsID, llvm::initializeHexagonBitSimplifyPass(), llvm::initializeHexagonConstExtendersPass(), llvm::initializeHexagonConstPropagationPass(), llvm::initializeHexagonEarlyIfConversionPass(), llvm::initializeHexagonExpandCondsetsPass(), llvm::initializeHexagonGenMuxPass(), llvm::initializeHexagonHardwareLoopsPass(), llvm::initializeHexagonLoopIdiomRecognizePass(), llvm::initializeHexagonNewValueJumpPass(), llvm::initializeHexagonOptAddrModePass(), llvm::initializeHexagonPacketizerPass(), llvm::initializeHexagonRDFOptPass(), llvm::initializeHexagonSplitDoubleRegsPass(), llvm::initializeHexagonVectorLoopCarriedReusePass(), llvm::initializeHexagonVExtractPass(), SchedCustomRegistry, llvm::ScheduleDAG::TII, llvm::SystemZISD::TM, and llvm::ScheduleDAG::TRI.

Referenced by llvm::HexagonTargetMachine::~HexagonTargetMachine().

◆ getEffectiveRelocModel()

|

static |

Definition at line 177 of file HexagonTargetMachine.cpp.

References llvm::Optional< T >::hasValue(), llvm::NVPTX::PTXCvtMode::RM, and llvm::Reloc::Static.

◆ LLVMInitializeHexagonTarget()

| void LLVMInitializeHexagonTarget | ( | ) |

Definition at line 183 of file HexagonTargetMachine.cpp.

References llvm::PassRegistry::getPassRegistry(), llvm::getTheHexagonTarget(), llvm::initializeHexagonBitSimplifyPass(), llvm::initializeHexagonConstExtendersPass(), llvm::initializeHexagonConstPropagationPass(), llvm::initializeHexagonEarlyIfConversionPass(), llvm::initializeHexagonGenMuxPass(), llvm::initializeHexagonHardwareLoopsPass(), llvm::initializeHexagonLoopIdiomRecognizePass(), llvm::initializeHexagonNewValueJumpPass(), llvm::initializeHexagonOptAddrModePass(), llvm::initializeHexagonPacketizerPass(), llvm::initializeHexagonRDFOptPass(), llvm::initializeHexagonSplitDoubleRegsPass(), llvm::initializeHexagonVectorLoopCarriedReusePass(), llvm::initializeHexagonVExtractPass(), and X.

Variable Documentation

◆ DisableAModeOpt

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ DisableHardwareLoops

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ DisableHCP

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ DisableHexagonCFGOpt

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ DisableHSDR

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ DisableStoreWidening

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableBitSimplify

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableCExtOpt

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableCommGEP

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableEarlyIf

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableExpandCondsets

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableGenExtract

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableGenInsert

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableGenMux

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableGenPred

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableInitialCFGCleanup

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableLoopPrefetch

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableLoopResched

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableRDFOpt

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableVectorPrint

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ EnableVExtractOpt

|

static |

Referenced by llvm::HexagonTargetMachine::createPassConfig().

◆ HexagonNoOpt

|

static |

◆ HexagonTargetMachineModule

| int HexagonTargetMachineModule = 0 |

HexagonTargetMachineModule - Note that this is used on hosts that cannot link in a library unless there are references into the library.

In particular, it seems that it is not possible to get things to work on Win32 without this. Though it is unused, do not remove it.

Definition at line 109 of file HexagonTargetMachine.cpp.

◆ SchedCustomRegistry

|

static |

Referenced by createVLIWMachineSched().

1.8.13

1.8.13