#include "Target/RISCV/MCTargetDesc/RISCVAsmBackend.h"

Public Member Functions | |

| RISCVAsmBackend (const MCSubtargetInfo &STI, uint8_t OSABI, bool Is64Bit) | |

| ~RISCVAsmBackend () override | |

| void | setForceRelocs () |

| bool | requiresDiffExpressionRelocations () const override |

| Check whether the given target requires emitting differences of two symbols as a set of relocations. More... | |

| void | applyFixup (const MCAssembler &Asm, const MCFixup &Fixup, const MCValue &Target, MutableArrayRef< char > Data, uint64_t Value, bool IsResolved, const MCSubtargetInfo *STI) const override |

Apply the Value for given Fixup into the provided data fragment, at the offset specified by the fixup and following the fixup kind as appropriate. More... | |

| std::unique_ptr< MCObjectTargetWriter > | createObjectTargetWriter () const override |

| bool | shouldForceRelocation (const MCAssembler &Asm, const MCFixup &Fixup, const MCValue &Target) override |

| Hook to check if a relocation is needed for some target specific reason. More... | |

| bool | fixupNeedsRelaxation (const MCFixup &Fixup, uint64_t Value, const MCRelaxableFragment *DF, const MCAsmLayout &Layout) const override |

| Simple predicate for targets where !Resolved implies requiring relaxation. More... | |

| bool | fixupNeedsRelaxationAdvanced (const MCFixup &Fixup, bool Resolved, uint64_t Value, const MCRelaxableFragment *DF, const MCAsmLayout &Layout, const bool WasForced) const override |

| Target specific predicate for whether a given fixup requires the associated instruction to be relaxed. More... | |

| unsigned | getNumFixupKinds () const override |

| Get the number of target specific fixup kinds. More... | |

| const MCFixupKindInfo & | getFixupKindInfo (MCFixupKind Kind) const override |

| Get information on a fixup kind. More... | |

| bool | mayNeedRelaxation (const MCInst &Inst, const MCSubtargetInfo &STI) const override |

| Check whether the given instruction may need relaxation. More... | |

| unsigned | getRelaxedOpcode (unsigned Op) const |

| void | relaxInstruction (const MCInst &Inst, const MCSubtargetInfo &STI, MCInst &Res) const override |

| Relax the instruction in the given fragment to the next wider instruction. More... | |

| bool | writeNopData (raw_ostream &OS, uint64_t Count) const override |

| Write an (optimal) nop sequence of Count bytes to the given output. More... | |

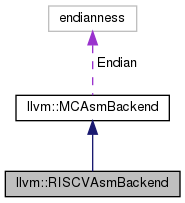

Public Member Functions inherited from llvm::MCAsmBackend Public Member Functions inherited from llvm::MCAsmBackend | |

| MCAsmBackend (const MCAsmBackend &)=delete | |

| MCAsmBackend & | operator= (const MCAsmBackend &)=delete |

| virtual | ~MCAsmBackend () |

| virtual void | reset () |

| lifetime management More... | |

| std::unique_ptr< MCObjectWriter > | createObjectWriter (raw_pwrite_stream &OS) const |

| Create a new MCObjectWriter instance for use by the assembler backend to emit the final object file. More... | |

| std::unique_ptr< MCObjectWriter > | createDwoObjectWriter (raw_pwrite_stream &OS, raw_pwrite_stream &DwoOS) const |

| Create an MCObjectWriter that writes two object files: a .o file which is linked into the final program and a .dwo file which is used by debuggers. More... | |

| virtual unsigned | getMinimumNopSize () const |

| Returns the minimum size of a nop in bytes on this target. More... | |

| virtual void | finishLayout (MCAssembler const &Asm, MCAsmLayout &Layout) const |

| Give backend an opportunity to finish layout after relaxation. More... | |

| virtual void | handleAssemblerFlag (MCAssemblerFlag Flag) |

| Handle any target-specific assembler flags. By default, do nothing. More... | |

| virtual uint32_t | generateCompactUnwindEncoding (ArrayRef< MCCFIInstruction >) const |

| Generate the compact unwind encoding for the CFI instructions. More... | |

| virtual bool | isMicroMips (const MCSymbol *Sym) const |

| Check whether a given symbol has been flagged with MICROMIPS flag. More... | |

| void | handleCodePaddingBasicBlockStart (MCObjectStreamer *OS, const MCCodePaddingContext &Context) |

| Handles all target related code padding when starting to write a new basic block to an object file. More... | |

| void | handleCodePaddingBasicBlockEnd (const MCCodePaddingContext &Context) |

| Handles all target related code padding after writing a block to an object file. More... | |

| void | handleCodePaddingInstructionBegin (const MCInst &Inst) |

| Handles all target related code padding before writing a new instruction to an object file. More... | |

| void | handleCodePaddingInstructionEnd (const MCInst &Inst) |

| Handles all target related code padding after writing an instruction to an object file. More... | |

| bool | relaxFragment (MCPaddingFragment *PF, MCAsmLayout &Layout) |

| Relaxes a fragment (changes the size of the padding) according to target requirements. More... | |

| virtual Optional< MCFixupKind > | getFixupKind (StringRef Name) const |

| Map a relocation name used in .reloc to a fixup kind. More... | |

Additional Inherited Members | |

Public Attributes inherited from llvm::MCAsmBackend Public Attributes inherited from llvm::MCAsmBackend | |

| const support::endianness | Endian |

Protected Member Functions inherited from llvm::MCAsmBackend Protected Member Functions inherited from llvm::MCAsmBackend | |

| MCAsmBackend (support::endianness Endian) | |

Detailed Description

Definition at line 24 of file RISCVAsmBackend.h.

Constructor & Destructor Documentation

◆ RISCVAsmBackend()

|

inline |

Definition at line 31 of file RISCVAsmBackend.h.

Referenced by llvm::createRISCVAsmBackend().

◆ ~RISCVAsmBackend()

|

inlineoverride |

Definition at line 34 of file RISCVAsmBackend.h.

Member Function Documentation

◆ applyFixup()

|

overridevirtual |

Apply the Value for given Fixup into the provided data fragment, at the offset specified by the fixup and following the fixup kind as appropriate.

Errors (such as an out of range fixup value) should be reported via Ctx. The STI is present only for fragments of type MCRelaxableFragment and MCDataFragment with hasInstructions() == true.

Implements llvm::MCAsmBackend.

Definition at line 263 of file RISCVAsmBackend.cpp.

References adjustFixupValue(), llvm::alignTo(), assert(), llvm::MCAssembler::getContext(), getFixupKindInfo(), llvm::MCFixup::getKind(), llvm::MCFixup::getOffset(), Info, llvm::ArrayRef< T >::size(), llvm::MCFixupKindInfo::TargetOffset, and llvm::MCFixupKindInfo::TargetSize.

Referenced by requiresDiffExpressionRelocations().

◆ createObjectTargetWriter()

|

overridevirtual |

Implements llvm::MCAsmBackend.

Definition at line 291 of file RISCVAsmBackend.cpp.

References llvm::createRISCVELFObjectWriter().

Referenced by requiresDiffExpressionRelocations().

◆ fixupNeedsRelaxation()

|

inlineoverridevirtual |

Simple predicate for targets where !Resolved implies requiring relaxation.

Implements llvm::MCAsmBackend.

Definition at line 55 of file RISCVAsmBackend.h.

References fixupNeedsRelaxationAdvanced(), and llvm_unreachable.

◆ fixupNeedsRelaxationAdvanced()

|

overridevirtual |

Target specific predicate for whether a given fixup requires the associated instruction to be relaxed.

Reimplemented from llvm::MCAsmBackend.

Definition at line 63 of file RISCVAsmBackend.cpp.

References llvm::RISCV::fixup_riscv_rvc_branch, llvm::RISCV::fixup_riscv_rvc_jump, and llvm::MCFixup::getKind().

Referenced by fixupNeedsRelaxation().

◆ getFixupKindInfo()

|

inlineoverridevirtual |

Get information on a fixup kind.

Reimplemented from llvm::MCAsmBackend.

Definition at line 71 of file RISCVAsmBackend.h.

References llvm::array_lengthof(), assert(), llvm::FirstTargetFixupKind, llvm::MCFixupKindInfo::FKF_IsPCRel, llvm::MCAsmBackend::getFixupKindInfo(), getNumFixupKinds(), getRelaxedOpcode(), mayNeedRelaxation(), llvm::RISCV::NumTargetFixupKinds, relaxInstruction(), and writeNopData().

Referenced by applyFixup().

◆ getNumFixupKinds()

|

inlineoverridevirtual |

Get the number of target specific fixup kinds.

Implements llvm::MCAsmBackend.

Definition at line 67 of file RISCVAsmBackend.h.

References llvm::RISCV::NumTargetFixupKinds.

Referenced by getFixupKindInfo().

◆ getRelaxedOpcode()

Definition at line 129 of file RISCVAsmBackend.cpp.

Referenced by getFixupKindInfo(), and mayNeedRelaxation().

◆ mayNeedRelaxation()

|

overridevirtual |

Check whether the given instruction may need relaxation.

- Parameters

-

Inst - The instruction to test. STI - The MCSubtargetInfo in effect when the instruction was encoded.

Implements llvm::MCAsmBackend.

Definition at line 143 of file RISCVAsmBackend.cpp.

References llvm::MCInst::getOpcode(), and getRelaxedOpcode().

Referenced by getFixupKindInfo().

◆ relaxInstruction()

|

overridevirtual |

Relax the instruction in the given fragment to the next wider instruction.

- Parameters

-

Inst The instruction to relax, which may be the same as the output. STI the subtarget information for the associated instruction. [out] Res On return, the relaxed instruction.

Implements llvm::MCAsmBackend.

Definition at line 91 of file RISCVAsmBackend.cpp.

References llvm::MCInst::addOperand(), llvm::MCOperand::createReg(), llvm::MCInst::getOpcode(), llvm::MCInst::getOperand(), llvm_unreachable, and llvm::MCInst::setOpcode().

Referenced by getFixupKindInfo().

◆ requiresDiffExpressionRelocations()

|

inlineoverridevirtual |

Check whether the given target requires emitting differences of two symbols as a set of relocations.

Reimplemented from llvm::MCAsmBackend.

Definition at line 41 of file RISCVAsmBackend.h.

References applyFixup(), llvm::HexStyle::Asm, createObjectTargetWriter(), llvm::Data, Fixup, llvm::MCSubtargetInfo::getFeatureBits(), and shouldForceRelocation().

◆ setForceRelocs()

|

inline |

Definition at line 36 of file RISCVAsmBackend.h.

Referenced by convertFPR32ToFPR64().

◆ shouldForceRelocation()

|

overridevirtual |

Hook to check if a relocation is needed for some target specific reason.

Reimplemented from llvm::MCAsmBackend.

Definition at line 28 of file RISCVAsmBackend.cpp.

References llvm::MCExpr::findAssociatedFragment(), llvm::RISCV::fixup_riscv_pcrel_hi20, llvm::RISCV::fixup_riscv_pcrel_lo12_i, llvm::RISCV::fixup_riscv_pcrel_lo12_s, llvm::MCAssembler::getContext(), llvm::MCSubtargetInfo::getFeatureBits(), llvm::MCFixup::getKind(), llvm::MCFixup::getLoc(), llvm::MCFixup::getValue(), llvm_unreachable, and llvm::MCContext::reportError().

Referenced by requiresDiffExpressionRelocations().

◆ writeNopData()

|

overridevirtual |

Write an (optimal) nop sequence of Count bytes to the given output.

If the target cannot generate such a sequence, it should return an error.

- Returns

- - True on success.

Implements llvm::MCAsmBackend.

Definition at line 148 of file RISCVAsmBackend.cpp.

References llvm::MCSubtargetInfo::getFeatureBits(), and llvm::raw_ostream::write().

Referenced by getFixupKindInfo().

The documentation for this class was generated from the following files:

- lib/Target/RISCV/MCTargetDesc/RISCVAsmBackend.h

- lib/Target/RISCV/MCTargetDesc/RISCVAsmBackend.cpp

1.8.13

1.8.13