This file implements the targeting of the RegisterBankInfo class for AArch64. More...

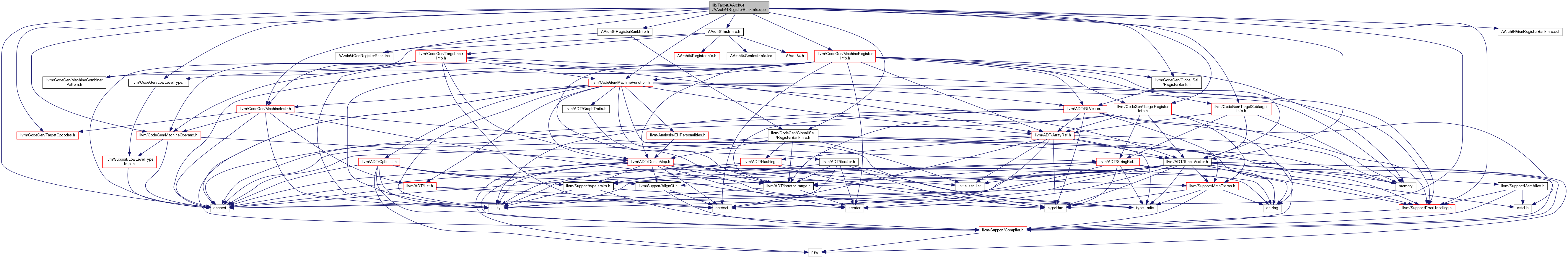

#include "AArch64RegisterBankInfo.h"#include "AArch64InstrInfo.h"#include "llvm/ADT/SmallVector.h"#include "llvm/CodeGen/GlobalISel/RegisterBank.h"#include "llvm/CodeGen/GlobalISel/RegisterBankInfo.h"#include "llvm/CodeGen/LowLevelType.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/TargetOpcodes.h"#include "llvm/CodeGen/TargetRegisterInfo.h"#include "llvm/CodeGen/TargetSubtargetInfo.h"#include "llvm/Support/ErrorHandling.h"#include <algorithm>#include <cassert>#include "AArch64GenRegisterBank.inc"#include "AArch64GenRegisterBankInfo.def"

Go to the source code of this file.

Macros | |

| #define | GET_TARGET_REGBANK_IMPL |

| #define | CHECK_PARTIALMAP(Idx, ValStartIdx, ValLength, RB) |

| #define | CHECK_VALUEMAP_IMPL(RBName, Size, Offset) |

| #define | CHECK_VALUEMAP(RBName, Size) CHECK_VALUEMAP_IMPL(RBName, Size, 0) |

| #define | CHECK_VALUEMAP_3OPS(RBName, Size) |

| #define | CHECK_VALUEMAP_CROSSREGCPY(RBNameDst, RBNameSrc, Size) |

| #define | CHECK_VALUEMAP_FPEXT(DstSize, SrcSize) |

Functions | |

| static bool | isPreISelGenericFloatingPointOpcode (unsigned Opc) |

Returns whether opcode Opc is a pre-isel generic floating-point opcode, having only floating-point operands. More... | |

Detailed Description

This file implements the targeting of the RegisterBankInfo class for AArch64.

- Todo:

- This should be generated by TableGen.

Definition in file AArch64RegisterBankInfo.cpp.

Macro Definition Documentation

◆ CHECK_PARTIALMAP

| #define CHECK_PARTIALMAP | ( | Idx, | |

| ValStartIdx, | |||

| ValLength, | |||

| RB | |||

| ) |

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo().

◆ CHECK_VALUEMAP

| #define CHECK_VALUEMAP | ( | RBName, | |

| Size | |||

| ) | CHECK_VALUEMAP_IMPL(RBName, Size, 0) |

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo().

◆ CHECK_VALUEMAP_3OPS

| #define CHECK_VALUEMAP_3OPS | ( | RBName, | |

| Size | |||

| ) |

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo().

◆ CHECK_VALUEMAP_CROSSREGCPY

| #define CHECK_VALUEMAP_CROSSREGCPY | ( | RBNameDst, | |

| RBNameSrc, | |||

| Size | |||

| ) |

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo().

◆ CHECK_VALUEMAP_FPEXT

| #define CHECK_VALUEMAP_FPEXT | ( | DstSize, | |

| SrcSize | |||

| ) |

Referenced by llvm::AArch64RegisterBankInfo::AArch64RegisterBankInfo().

◆ CHECK_VALUEMAP_IMPL

| #define CHECK_VALUEMAP_IMPL | ( | RBName, | |

| Size, | |||

| Offset | |||

| ) |

◆ GET_TARGET_REGBANK_IMPL

| #define GET_TARGET_REGBANK_IMPL |

Definition at line 32 of file AArch64RegisterBankInfo.cpp.

Function Documentation

◆ isPreISelGenericFloatingPointOpcode()

Returns whether opcode Opc is a pre-isel generic floating-point opcode, having only floating-point operands.

Definition at line 383 of file AArch64RegisterBankInfo.cpp.

References assert(), llvm::RegisterBankInfo::DefaultMappingID, llvm::RegisterBankInfo::getInstructionMapping(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::AArch64GenRegisterBankInfo::getRegBankBaseIdxOffset(), llvm::MachineFunction::getRegInfo(), llvm::LLT::getSizeInBits(), llvm::MachineRegisterInfo::getType(), llvm::AArch64GenRegisterBankInfo::getValueMapping(), llvm::LLT::isVector(), MI, MRI, llvm::AArch64GenRegisterBankInfo::PMI_FirstFPR, llvm::AArch64GenRegisterBankInfo::PMI_FirstGPR, and Size.

Referenced by llvm::AArch64RegisterBankInfo::getInstrMapping().

1.8.13

1.8.13