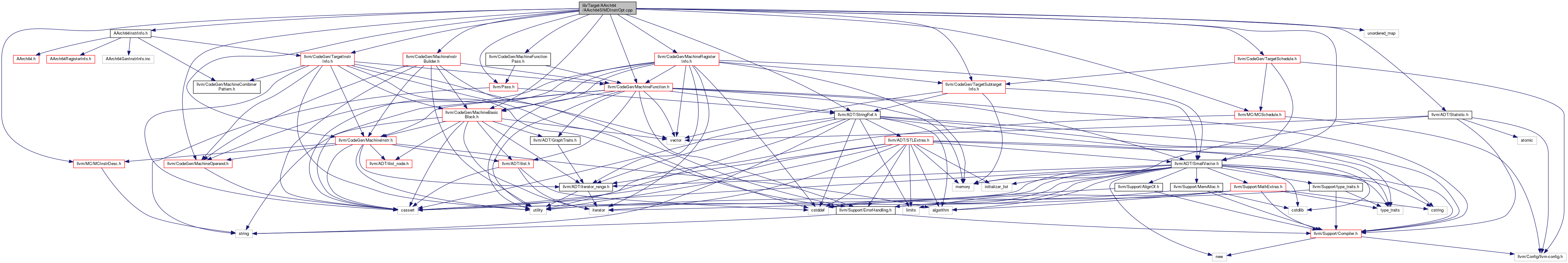

#include "AArch64InstrInfo.h"#include "llvm/ADT/SmallVector.h"#include "llvm/ADT/Statistic.h"#include "llvm/ADT/StringRef.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/TargetInstrInfo.h"#include "llvm/CodeGen/TargetSchedule.h"#include "llvm/CodeGen/TargetSubtargetInfo.h"#include "llvm/MC/MCInstrDesc.h"#include "llvm/MC/MCSchedule.h"#include "llvm/Pass.h"#include <unordered_map>

Go to the source code of this file.

Macros | |

| #define | DEBUG_TYPE "aarch64-simdinstr-opt" |

| #define | AARCH64_VECTOR_BY_ELEMENT_OPT_NAME "AArch64 SIMD instructions optimization pass" |

| #define | RuleST2(OpcOrg, OpcR0, OpcR1, OpcR2, RC) {OpcOrg, {OpcR0, OpcR1, OpcR2}, RC} |

| #define | RuleST4(OpcOrg, OpcR0, OpcR1, OpcR2, OpcR3, OpcR4, OpcR5, OpcR6, OpcR7, OpcR8, OpcR9, RC) |

Functions | |

| STATISTIC (NumModifiedInstr, "Number of SIMD instructions modified") | |

| INITIALIZE_PASS (AArch64SIMDInstrOpt, "aarch64-simdinstr-opt", AARCH64_VECTOR_BY_ELEMENT_OPT_NAME, false, false) bool AArch64SIMDInstrOpt | |

| Based only on latency of instructions, determine if it is cost efficient to replace the instruction InstDesc by the instructions stored in the array InstDescRepl. More... | |

Macro Definition Documentation

◆ AARCH64_VECTOR_BY_ELEMENT_OPT_NAME

| #define AARCH64_VECTOR_BY_ELEMENT_OPT_NAME "AArch64 SIMD instructions optimization pass" |

Definition at line 62 of file AArch64SIMDInstrOpt.cpp.

◆ DEBUG_TYPE

| #define DEBUG_TYPE "aarch64-simdinstr-opt" |

Definition at line 57 of file AArch64SIMDInstrOpt.cpp.

◆ RuleST2

| #define RuleST2 | ( | OpcOrg, | |

| OpcR0, | |||

| OpcR1, | |||

| OpcR2, | |||

| RC | |||

| ) | {OpcOrg, {OpcR0, OpcR1, OpcR2}, RC} |

Definition at line 94 of file AArch64SIMDInstrOpt.cpp.

◆ RuleST4

| #define RuleST4 | ( | OpcOrg, | |

| OpcR0, | |||

| OpcR1, | |||

| OpcR2, | |||

| OpcR3, | |||

| OpcR4, | |||

| OpcR5, | |||

| OpcR6, | |||

| OpcR7, | |||

| OpcR8, | |||

| OpcR9, | |||

| RC | |||

| ) |

Definition at line 96 of file AArch64SIMDInstrOpt.cpp.

Function Documentation

◆ INITIALIZE_PASS()

| INITIALIZE_PASS | ( | AArch64SIMDInstrOpt | , |

| "aarch64-simdinstr-opt" | , | ||

| AARCH64_VECTOR_BY_ELEMENT_OPT_NAME | , | ||

| false | , | ||

| false | |||

| ) |

Based only on latency of instructions, determine if it is cost efficient to replace the instruction InstDesc by the instructions stored in the array InstDescRepl.

Return true if replacement is expected to be faster.

Definition at line 211 of file AArch64SIMDInstrOpt.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), assert(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::SmallVectorImpl< T >::clear(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::getKillRegState(), llvm::MachineInstr::getNumOperands(), llvm::MCInstrDesc::getOpcode(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineFunction::getSubtarget(), I, llvm::MachineOperand::isImm(), llvm::MachineOperand::isKill(), llvm::MCSchedClassDesc::isValid(), llvm::MCSchedClassDesc::isVariant(), llvm_unreachable, llvm::Match, MI, MRI, llvm::SmallVectorTemplateBase< T >::push_back(), llvm::ARM_MB::ST, and TII.

◆ STATISTIC()

| STATISTIC | ( | NumModifiedInstr | , |

| "Number of SIMD instructions modified" | |||

| ) |

1.8.13

1.8.13