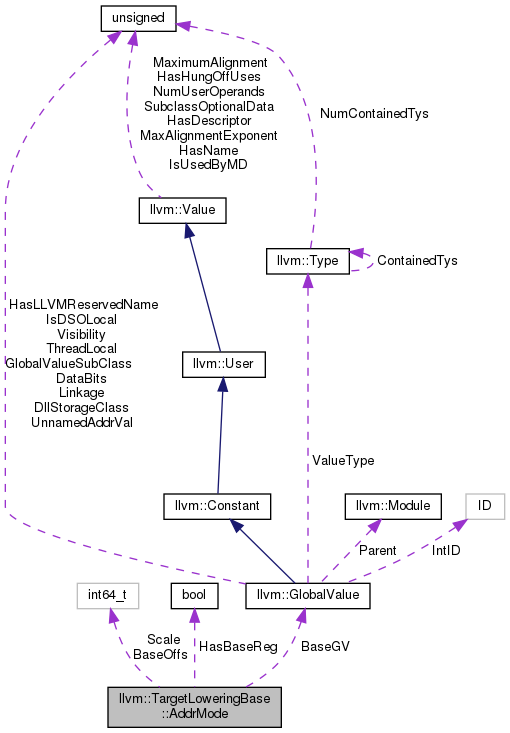

This represents an addressing mode of: BaseGV + BaseOffs + BaseReg + Scale*ScaleReg If BaseGV is null, there is no BaseGV. More...

#include "llvm/CodeGen/TargetLowering.h"

Public Member Functions | |

| AddrMode ()=default | |

Public Attributes | |

| GlobalValue * | BaseGV = nullptr |

| int64_t | BaseOffs = 0 |

| bool | HasBaseReg = false |

| int64_t | Scale = 0 |

Detailed Description

This represents an addressing mode of: BaseGV + BaseOffs + BaseReg + Scale*ScaleReg If BaseGV is null, there is no BaseGV.

If BaseOffs is zero, there is no base offset. If HasBaseReg is false, there is no base register. If Scale is zero, there is no ScaleReg. Scale of 1 indicates a reg with no scale.

Definition at line 2068 of file TargetLowering.h.

Constructor & Destructor Documentation

◆ AddrMode()

|

default |

Member Data Documentation

◆ BaseGV

| GlobalValue* llvm::TargetLoweringBase::AddrMode::BaseGV = nullptr |

Definition at line 2069 of file TargetLowering.h.

Referenced by llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getScalingFactorCost(), llvm::MipsTargetLowering::getTypeForExtReturn(), INITIALIZE_PASS(), llvm::RISCVTargetLowering::isLegalAddressingMode(), llvm::AVRTargetLowering::isLegalAddressingMode(), llvm::XCoreTargetLowering::isLegalAddressingMode(), llvm::SITargetLowering::isLegalAddressingMode(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isLegalAddressingMode(), llvm::HexagonTargetLowering::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::AArch64TargetLowering::isLegalAddressingMode(), llvm::SystemZTargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::isLegalAddressingMode(), llvm::PPCTargetLowering::isLegalAddressingMode(), llvm::X86TargetLowering::isLegalAddressingMode(), and llvm::TargetLoweringBase::isLegalAddressingMode().

◆ BaseOffs

| int64_t llvm::TargetLoweringBase::AddrMode::BaseOffs = 0 |

Definition at line 2070 of file TargetLowering.h.

Referenced by canMoveInstsAcrossMemOp(), llvm::SITargetLowering::getAddrModeArguments(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getScalingFactorCost(), INITIALIZE_PASS(), llvm::RISCVTargetLowering::isLegalAddressingMode(), llvm::AVRTargetLowering::isLegalAddressingMode(), llvm::XCoreTargetLowering::isLegalAddressingMode(), llvm::SITargetLowering::isLegalAddressingMode(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isLegalAddressingMode(), llvm::HexagonTargetLowering::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::AArch64TargetLowering::isLegalAddressingMode(), llvm::SystemZTargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::isLegalAddressingMode(), llvm::PPCTargetLowering::isLegalAddressingMode(), llvm::X86TargetLowering::isLegalAddressingMode(), llvm::TargetLoweringBase::isLegalAddressingMode(), and llvm::SITargetLowering::isLegalGlobalAddressingMode().

◆ HasBaseReg

Definition at line 2071 of file TargetLowering.h.

Referenced by canMoveInstsAcrossMemOp(), getFPTernOp(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getScalingFactorCost(), llvm::MipsTargetLowering::getTypeForExtReturn(), INITIALIZE_PASS(), llvm::RISCVTargetLowering::isLegalAddressingMode(), llvm::AVRTargetLowering::isLegalAddressingMode(), llvm::XCoreTargetLowering::isLegalAddressingMode(), llvm::SITargetLowering::isLegalAddressingMode(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::AArch64TargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::isLegalAddressingMode(), llvm::PPCTargetLowering::isLegalAddressingMode(), llvm::X86TargetLowering::isLegalAddressingMode(), llvm::TargetLoweringBase::isLegalAddressingMode(), llvm::SITargetLowering::isLegalGlobalAddressingMode(), llvm::ARMTargetLowering::isLegalT1ScaledAddressingMode(), and llvm::ARMTargetLowering::isLegalT2ScaledAddressingMode().

◆ Scale

| int64_t llvm::TargetLoweringBase::AddrMode::Scale = 0 |

Definition at line 2072 of file TargetLowering.h.

Referenced by llvm::SITargetLowering::getAddrModeArguments(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::getScalingFactorCost(), llvm::ARMTargetLowering::getScalingFactorCost(), llvm::AArch64TargetLowering::getScalingFactorCost(), llvm::X86TargetLowering::getScalingFactorCost(), llvm::MipsTargetLowering::getTypeForExtReturn(), llvm::RISCVTargetLowering::isLegalAddressingMode(), llvm::ARCTargetLowering::isLegalAddressingMode(), llvm::AVRTargetLowering::isLegalAddressingMode(), llvm::XCoreTargetLowering::isLegalAddressingMode(), llvm::SITargetLowering::isLegalAddressingMode(), llvm::BasicTTIImplBase< AMDGPUTTIImpl >::isLegalAddressingMode(), llvm::HexagonTargetLowering::isLegalAddressingMode(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::AArch64TargetLowering::isLegalAddressingMode(), llvm::SystemZTargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::isLegalAddressingMode(), llvm::PPCTargetLowering::isLegalAddressingMode(), llvm::X86TargetLowering::isLegalAddressingMode(), llvm::TargetLoweringBase::isLegalAddressingMode(), llvm::SITargetLowering::isLegalGlobalAddressingMode(), llvm::ARMTargetLowering::isLegalT1ScaledAddressingMode(), and llvm::ARMTargetLowering::isLegalT2ScaledAddressingMode().

The documentation for this struct was generated from the following file:

- include/llvm/CodeGen/TargetLowering.h

1.8.13

1.8.13