Include dependency graph for SchedulerRegistry.h:

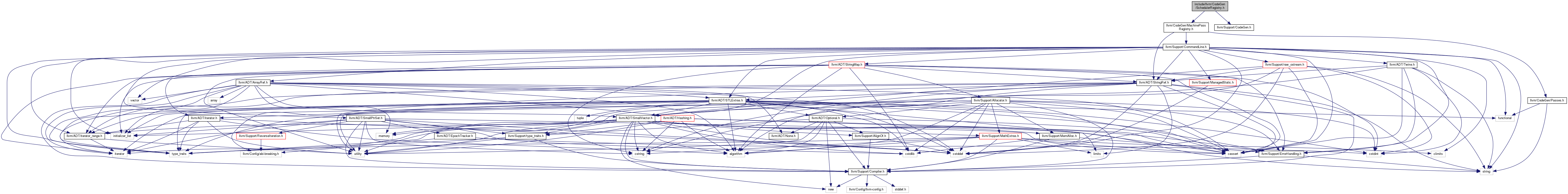

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| class | llvm::RegisterScheduler |

Namespaces | |

| llvm | |

| This class represents lattice values for constants. | |

Functions | |

| ScheduleDAGSDNodes * | llvm::createBURRListDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createBURRListDAGScheduler - This creates a bottom up register usage reduction list scheduler. More... | |

| ScheduleDAGSDNodes * | llvm::createSourceListDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createBURRListDAGScheduler - This creates a bottom up list scheduler that schedules nodes in source code order when possible. More... | |

| ScheduleDAGSDNodes * | llvm::createHybridListDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level) |

| createHybridListDAGScheduler - This creates a bottom up register pressure aware list scheduler that make use of latency information to avoid stalls for long latency instructions in low register pressure mode. More... | |

| ScheduleDAGSDNodes * | llvm::createILPListDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level) |

| createILPListDAGScheduler - This creates a bottom up register pressure aware list scheduler that tries to increase instruction level parallelism in low register pressure mode. More... | |

| ScheduleDAGSDNodes * | llvm::createFastDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createFastDAGScheduler - This creates a "fast" scheduler. More... | |

| ScheduleDAGSDNodes * | llvm::createVLIWDAGScheduler (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createVLIWDAGScheduler - Scheduler for VLIW targets. More... | |

| ScheduleDAGSDNodes * | llvm::createDefaultScheduler (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createDefaultScheduler - This creates an instruction scheduler appropriate for the target. More... | |

| ScheduleDAGSDNodes * | llvm::createDAGLinearizer (SelectionDAGISel *IS, CodeGenOpt::Level OptLevel) |

| createDAGLinearizer - This creates a "no-scheduling" scheduler which linearize the DAG using topological order. More... | |

1.8.13

1.8.13